Động cơ servo

Nâng cao Hiệu suất Bằng FPGA và DSP: Chìa khóa Tối ưu hóa Vòng Điều khiển Servo Thời gian Thực

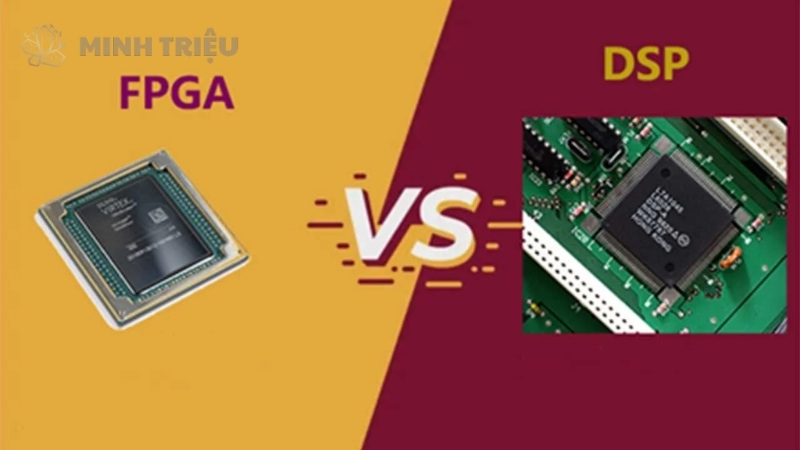

Động cơ servo hiện đại yêu cầu tốc độ, độ chính xác và điều khiển thời gian thực cao, trong khi MCU hoặc CPU truyền thống giới hạn băng thông và gây trễ pha. FPGA và DSP cung cấp giải pháp tối ưu: FPGA xử lý song song cực nhanh, DSP đảm nhiệm xử lý tín hiệu số phức tạp, giúp nâng cao hiệu suất động lực học. Kết hợp FPGA và DSP cho phép thiết kế vòng điều khiển servo tiên tiến, đạt tốc độ và độ chính xác cao, phù hợp với yêu cầu khắt khe của sản xuất công nghiệp 4.0. Bài viết này sẽ phân tích vai trò then chốt của FPGA và DSP trong việc thiết kế vòng điều khiển servo tiên tiến và tốc độ cao.

1. Giới hạn của Điều khiển Servo Truyền thống

1.1. Giới hạn về Tốc độ và Trễ (Latency)

Điều khiển servo truyền thống gặp phải giới hạn nghiêm trọng về tốc độ chu kỳ điều khiển do kiến trúc tuần tự của CPU/MCU đơn nhân. Kiến trúc tuần tự buộc phải thực hiện toàn bộ các phép tính toán của vòng điều khiển servo bao gồm thu thập phản hồi Encoder, chuyển đổi Clarke/Park, tính toán PID, và tạo xung PWM theo một trình tự cố định. Điều này tạo ra độ trễ cố hữu (Latency) và trễ pha đáng kể trong chu kỳ điều khiển (thường là 5 kHz đến 10 kHz). Trễ pha là nguyên nhân chính làm giảm Biên độ Pha (Phase Margin) của hệ thống. Kỹ sư buộc phải giảm độ lợi (Gain) của bộ điều khiển để duy trì sự ổn định, dẫn đến băng thông điều khiển thấp và khả năng đáp ứng động lực học kém.

1.2. Thách thức của Việc Tích hợp Thuật toán Phức tạp

Việc tích hợp các thuật toán phức tạp gặp thách thức lớn khi cần chạy đồng thời và đủ nhanh trên một nhân xử lý CPU/MCU giới hạn. Các thuật toán nâng cao, cần thiết cho việc tối ưu hóa hiệu suất hiện đại như bộ lọc thích ứng (Adaptive Filters) để khử rung chấn, bộ quan sát (Observers) để ước tính tải hoặc mô-men xoắn, và các phương pháp hiệu chỉnh phi tuyến tính đòi hỏi tài nguyên tính toán dấu phẩy động rất lớn.

CPU/MCU truyền thống thường phải kéo dài chu kỳ điều khiển hoặc hy sinh độ chính xác tính toán để chạy các tác vụ này. Điều này dẫn đến lỗi theo dõi (Tracking Error) và rung chấn không thể kiểm soát, vì tốc độ Điều khiển thời gian thực không đáp ứng kịp sự thay đổi của động lực học cơ khí.

Một số thuật toán phức tạp gặp thách thức khi triển khai trên MCU truyền thống:

- Bộ lọc Notch Thích ứng: Cần liên tục phân tích FFT mini để tìm tần số cộng hưởng thay đổi.

- Lựa chọn Vector Tối ưu (SVM-PWM): Đòi hỏi tính toán lượng giác và chuyển đổi tọa độ nhanh trong vòng dòng điện.

- Quan sát Tải (Load Observer): Yêu cầu vi phân và tính toán ma trận để ước tính mô-men xoắn tải, cần thực hiện ở tần số cao.

- Điều khiển Phi tuyến tính: Các mô hình điều khiển tiên tiến đòi hỏi độ chính xác dấu phẩy động và tốc độ tính toán lớn, thường vượt quá khả năng của MCU cơ bản.

2. Vai trò của Bộ xử lý Tín hiệu Số (DSP) trong Servo Drive

2.1. Sức mạnh Xử lý Tín hiệu Số

DSP cung cấp sức mạnh tính toán vượt trội nhờ kiến trúc được thiết kế chuyên biệt để xử lý tín hiệu số (Digital Signal Processing). Kiến trúc của DSP bao gồm các đơn vị MAC (Multiply-Accumulate) chuyên dụng, cấu trúc bộ nhớ Harvard (tách biệt chương trình và dữ liệu) và các cơ chế đường ống (pipelining) sâu.

Điều này cho phép DSP thực hiện hàng trăm phép nhân và cộng chỉ trong một chu kỳ đồng hồ, làm cho nó trở nên lý tưởng cho các tác vụ lặp lại và chuyên sâu về toán học. Khả năng này là thiết yếu cho các thuật toán điều khiển FOC tốc độ cao và việc triển khai các bộ lọc kỹ thuật số phức tạp. DSP thường sử dụng tính toán dấu phẩy động để duy trì độ chính xác cao.

2.2. Ứng dụng DSP trong Vòng Điều khiển

DSP đảm nhận vai trò quan trọng trong tính toán Vòng Tốc độ (Velocity Loop) và Vòng Vị trí (Position Loop), nơi yêu cầu xử lý phức tạp hơn so với Vòng Dòng điện (Current Loop). Khả năng thực thi nhanh và chính xác các thuật toán FOC giúp tạo mô-men xoắn tối ưu, nâng cao hiệu suất và độ chính xác vận hành của động cơ servo. DSP là yếu tố then chốt để đảm bảo các vòng điều khiển cao cấp vận hành ổn định và đáp ứng thời gian thực trong môi trường sản xuất công nghiệp.

3. Tác động Đột phá của FPGA lên Hiệu suất Servo

3.1. Nguyên lý Hoạt động Song song của FPGA

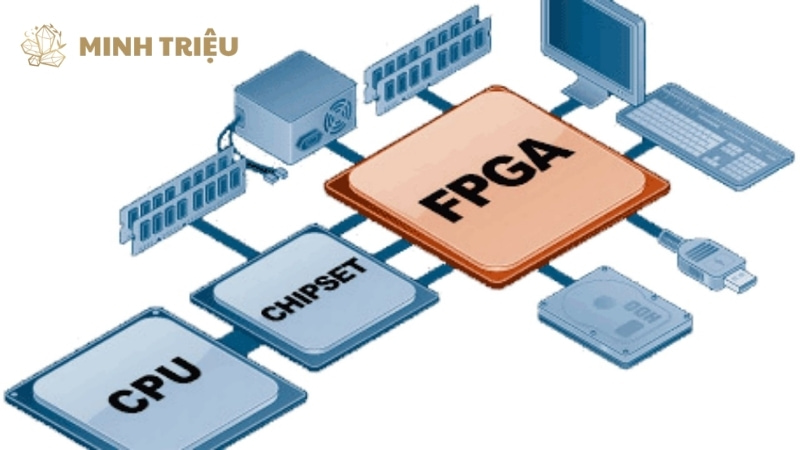

FPGA tạo ra tác động đột phá nhờ nguyên lý hoạt động hoàn toàn song song (True Parallelism) dựa trên logic cấu hình lại. Kiến trúc của FPGA sử dụng hàng nghìn khối logic (LUTs) và Flip-Flops (FFs), cho phép kỹ sư thiết kế một mạch điện tử tùy chỉnh. Điều này khác biệt hoàn toàn so với kiến trúc tuần tự của CPU/DSP. Bằng cách thực hiện các tác vụ tính toán đồng thời trên phần cứng, FPGA giúp độ trễ gần như bằng không (Ultra-low latency), cung cấp thời gian chu kỳ điều khiển chỉ tính bằng nanô giây (ns).

3.2. Ứng dụng FPGA trong Điều khiển Servo Tốc độ Cao

FPGA được ứng dụng chủ yếu để xử lý các tác vụ lặp đi lặp lại, cực kỳ nhạy cảm với thời gian, và yêu cầu Điều khiển thời gian thực nhanh nhất. FPGA thực hiện Vòng Dòng điện ở tần số cực cao (100 kHz đến 200 kHz), vượt xa khả năng của DSP. FPGA cũng xử lý các giao diện Encoder tốc độ cao trực tiếp bằng phần cứng với trễ pha gần bằng 0. Việc này đảm bảo tín hiệu phản hồi được thu thập và xử lý tức thời, giúp nâng cao hiệu suất tổng thể và băng thông điều khiển lên mức tối đa.

Các ứng dụng quan trọng của FPGA trong vòng điều khiển servo bao gồm:

- Xử lý Phản hồi Encoder: Đếm xung (Incremental) và giải mã giao tiếp nối tiếp tốc độ cao (Serial protocols) như EnDAT/BiSS/Hiperface DSL.

- Tạo Xung PWM: Tạo ra các xung PWM (Pulse Width Modulation) với độ phân giải cao và ít bị Jitter (dao động thời gian), nâng cao chất lượng nguồn cấp và giảm tổn thất năng lượng.

- Bộ lọc FIR/IIR Nhanh: Thực hiện các bộ lọc kỹ thuật số tuyến tính đơn giản trực tiếp bằng phần cứng để khử nhiễu tức thời trong Vòng Dòng điện.

- Chuyển đổi Tọa độ (Clarke/Park): Thực hiện các phép tính FOC cơ bản để tạo lệnh mô-men xoắn, đảm bảo tốc độ phản ứng cực nhanh cho Vòng Dòng điện.

4. Tối ưu hóa Hiệu suất nhờ Sự Cộng hưởng giữa FPGA và DSP

4.1. Phân chia Tác vụ Thông minh

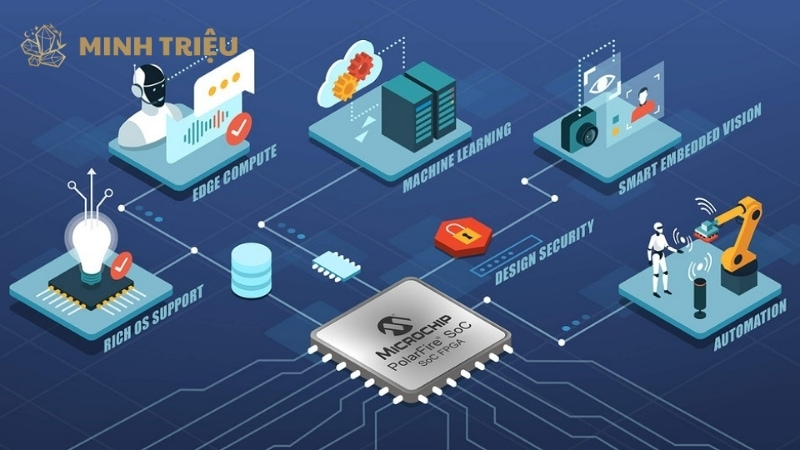

Sự cộng hưởng giữa FPGA và DSP được thực hiện thông qua chiến lược phân chia tác vụ thông minh (Intelligent Task Partitioning), khai thác điểm mạnh riêng biệt của mỗi kiến trúc. FPGA đảm nhận các tác vụ quan trọng về thời gian (Critical Timing), lặp đi lặp lại và yêu cầu độ trễ thấp nhất. Điều này bao gồm Vòng Dòng điện (thường là 100 kHz+), giao tiếp phần cứng, và xử lý phản hồi từ Encoder.

DSP xử lý các thuật toán phức tạp, đòi hỏi khả năng dấu phẩy động chính xác, và linh hoạt về phần mềm. Điều này bao gồm Vòng Tốc độ và Vòng Vị trí (thường là 1-10 kHz), các thuật toán tự động điều chỉnh Gain/Auto-Tuning, và giao tiếp cấp cao qua bus truyền thông công nghiệp. Sự kết hợp này mang lại lợi ích kép: tối đa hóa băng thông điều khiển thông qua tốc độ của FPGA trong khi vẫn duy trì sự linh hoạt và khả năng xử lý tín hiệu số phức tạp của DSP.

4.2. Tác động đến Hiệu suất Động lực học

Phân chia tác vụ tác động trực tiếp đến hiệu suất động lực học bằng cách tăng đáng kể băng thông điều khiển của hệ thống. Vòng dòng điện nhanh hơn (FPGA) cung cấp một phản ứng mô-men xoắn tức thời và chính xác hơn cho Vòng Tốc độ (DSP). Điều này giúp hệ thống giảm Jerk và rung chấn không mong muốn.

Tác động này được đo lường bằng các chỉ số hiệu suất:

- Tăng Băng thông Điều khiển: Tăng khả năng đáp ứng với lệnh thay đổi vị trí/tốc độ.

- Giảm Thời gian Ổn định (Settling Time): Giảm thời gian cần thiết để đạt độ chính xác mục tiêu.

- Khả năng Chống nhiễu: Cải thiện khả năng chống lại các dao động và nhiễu bên ngoài.

Tối ưu hóa vòng điều khiển servo dựa trên nền tảng FPGA và DSP cho phép nâng cao hiệu suất động lực học lên gấp 2 đến 3 lần so với kiến trúc MCU truyền thống.

5. Ứng dụng Thực tiễn và Lợi ích Kinh tế

5.1. Ứng dụng Công nghiệp Tiêu biểu

Các ứng dụng công nghiệp tiêu biểu sử dụng công nghệ FPGA và DSP bao gồm những hệ thống đòi hỏi tốc độ và độ chính xác tuyệt đối.

- Máy móc Tốc độ cao (Pick-and-Place, Bao bì): Các máy này yêu cầu thời gian chu kỳ máy (Cycle Time) cực ngắn. Điều khiển thời gian thực tốc độ cao giúp giảm thời gian ổn định của từng lần đặt/lấy.

- Máy Công cụ CNC độ chính xác cao: Các máy này yêu cầu độ chính xác tuyệt đối để đảm bảo độ mịn bề mặt và dung sai kích thước. FPGA đảm bảo băng thông điều khiển đủ rộng để phản ứng tức thời với tải cắt.

- Robot Cộng tác (Cobots) và Robot song song (Parallel Robots): Yêu cầu điều khiển thời gian thực đa trục để đồng bộ hóa chuyển động phức tạp. FPGA cung cấp độ trễ thấp cần thiết để đồng bộ hóa hoàn hảo các khớp robot.

5.2. Phân tích Lợi ích

Lợi ích kinh tế từ việc áp dụng FPGA và DSP là rất lớn, chủ yếu thông qua việc nâng cao hiệu suất và độ bền hệ thống. Nâng cao hiệu suất dẫn đến tăng thông lượng sản xuất bằng cách giảm thời gian ổn định và cho phép máy hoạt động ở tốc độ cao hơn. Ví dụ: việc giảm thời gian ổn định từ 50 ms xuống 10 ms có thể tăng năng suất lên 10-30% tùy thuộc vào ứng dụng.

| Chỉ số Hiệu suất | Hệ thống MCU/CPU Truyền thống | Hệ thống FPGA & DSP Cộng hưởng | Mức độ Nâng cao hiệu suất |

| Tần số Vòng Dòng điện | 5 kHz – 10 kHz | 100 kHz – 200 kHz | 20 – 40 lần |

| Băng thông Điều khiển | 50 Hz – 150 Hz | 200 Hz – 500 Hz+ | 2 – 5 lần |

| Độ trễ Vòng Điều khiển | 50 µs – 200 µs | Dưới 5 µs (Vòng dòng điện) | Giảm 90% – 99% |

| Độ chính xác Vị trí | Bị ảnh hưởng bởi trễ pha và rung chấn | Tối ưu hóa bởi độ trễ thấp và bộ lọc nâng cao | Tăng 50% – 100% |

6. Kết luận

Chiến lược kết hợp FPGA và DSP tối ưu hóa hiệu suất động cơ servo: FPGA xử lý thời gian thực cho vòng dòng điện, DSP đảm nhiệm xử lý tín hiệu số cho vòng điều khiển cao cấp, nâng băng thông và độ chính xác. Xu hướng tiếp theo là tích hợp AI/Machine Learning để Servo Drive tự học đặc tính cơ khí, tự tối ưu thông số điều khiển và bộ lọc theo thời gian thực, giúp duy trì lợi thế về hiệu suất và độ chính xác trong sản xuất công nghiệp.